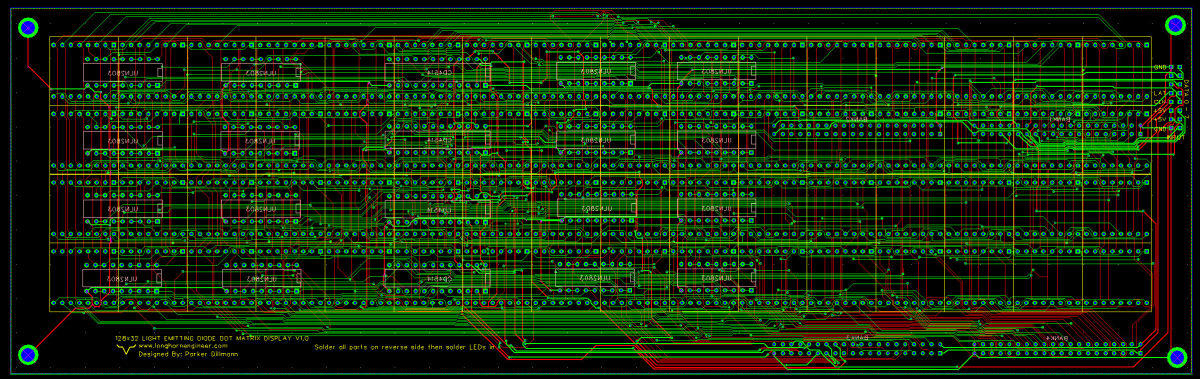

The old program took to make Logic elements to fit. Now it uses a 2-port RAM element to replace the huge registers. The protocol for shifting in is a bit different now. Instead of shifting in all the data at once and then Latching the user shifts in the data 64 bits at a time then latches.

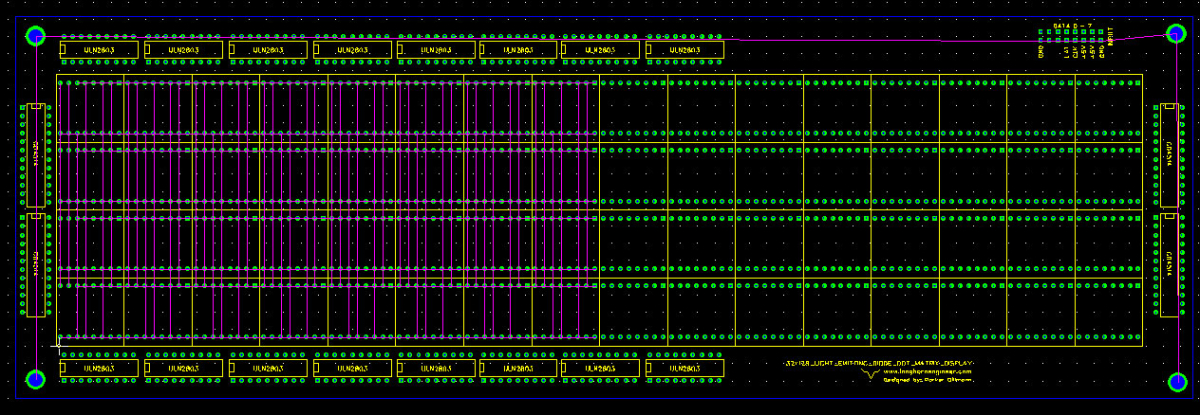

module LED_Matrix_32x128

(

clk,e_cnt,row_cnt,col,SDRAM_CS,SRAM_CS,LAT,INPUT,SCLK

);

input wire clk;

input wire LAT;

input wire [7:0] INPUT;

input wire SCLK;

output reg [63:0] col;

output reg [0:0] SDRAM_CS;

output reg [0:0] SRAM_CS;

output reg [5:0] row_cnt;

output reg [4:0] e_cnt;

reg [24:0] clk_slow;

reg [63:0] col_buffer;

reg [5:0] read_addr;

reg [5:0] write_addr;

reg [63:0] disp_mem_data;

reg disp_mem_wren;

wire [63:0] disp_mem_q;

initial

begin

SDRAM_CS <= 1'b0;

SRAM_CS <= 1'b0;

clk_slow <= 16'b0000000000000000;

row_cnt <= 5'b00000;

e_cnt <= 4'b1000;

write_addr <= 5'b00000;

disp_mem_wren <= 0;

end

always @(posedge clk)

begin

clk_slow <= clk_slow + 1'b1;

end

always @(posedge clk_slow[10])

begin

if(row_cnt > 5'b01111)

begin

row_cnt <= 5'b00000;

e_cnt <= {e_cnt[2:0],e_cnt[3]};

end

col <= disp_mem_q;

row_cnt <= row_cnt + 1'b1;

read_addr <= read_addr + 1'b1;

end

always @(posedge SCLK)

begin

if(LAT)

begin

col_buffer <= {col_buffer[62:0],INPUT[0]};

end

else

begin

disp_mem_data <= col_buffer;

disp_mem_wren <= 1;

disp_mem_wren <= 0;

write_addr <= write_addr + 1'b1;

end

end

display_memory disp_mem_inst (

.rdaddress (read_addr),

.wraddress (write_addr),

.clock (clk),

.data (disp_mem_data),

.wren (disp_mem_wren),

.q (disp_mem_q)

);

endmodule